Soitec ist ein europäischer Tech-Champion und aktuell das einzige Unternehmen aus der Halbleiterindustrie im 10xDNA-Portfolio. Es hat sich auf eine Technologie spezialisiert, die aus unserer Sicht über die kommenden Jahre massiv an Bedeutung in der Chipherstellung gewinnen wird. In diesem Artikel stellen wir das Unternehmen und seine Technologie vor und erläutern außerdem unsere Investmenthypothesen, die der Aufnahme ins 10xDNA-Portfolio zugrunde liegen. Eine Zusammenfassung des Artikels findet ihr auch in unserem Video auf Youtube.

9:58

Was macht Soitec?

Soitec wurde 1992 in Grenoble, Frankreich, gegründet als Spin-Off des dort ansässigen CEA-Leti, einem staatlichen Forschungsinstitut für Elektronik und Informationstechnologie. Es hat bereits eine bewegte Geschichte hinter sich, in der es u.a. Photovoltaiksysteme, LED-Lichtsysteme und Ausrüstung für die Halbleiterproduktion gefertigt hat. All diese Geschäftsbereiche waren irgendwann jedoch nicht mehr profitabel und wurden bei der strategischen Neuausrichtung 2016 durch CEO Paul Boudre abgestoßen. Inzwischen fokussiert sich Soitec nur noch auf seine absolute Kernkompetenz: die Herstellung von Silicon-on-Insulator-Wafern (SOI-Wafer, zu deutsch: Silizium-auf-Isolator-Wafer) für die Halbleiterindustrie. Was es genau mit dieser speziellen Art von Wafern auf sich hat, erläutern wir weiter unten im Detail.

Nachdem Soitec vor dem Strategiewechsel beinahe in die Insolvenz gelaufen wäre, geht es seit der Neuausrichtung mit dem Unternehmen wieder steil bergauf und der Umsatz hat sich von 233 Millionen Euro in Fiskaljahr 2016 auf 863 Millionen Euro in Fiskaljahr 2022 vervielfacht. Gleichzeitig wurde 2017 nach neun Jahren Verlust zum ersten Mal wieder ein positives Nettoeinkommen erzielt, welches sich seitdem ebenfalls stark erhöht hat. Für das Fiskaljahr 2026 hat Soitec ein Umsatzziel von über 2 Mrd. € bei einer EBITDA-Marge von 40% ausgegeben.

Heute hat Soitec mehr als 2.000 Mitarbeiter und Fabriken in Frankreich, Belgien, Singapur und China. Soitecs Produkte bleiben von der Öffentlichkeit meist unbemerkt, sind jedoch ein essentieller Grundbaustein für viele komplexe Anwendungen und Produkte der Halbleiterindustrie. Beispielsweise finden sich heute in praktisch jedem produzierten Smartphone (u.a. Apples iPhone und Googles Pixel Phone) und in der Leistungselektronik vieler Elektroautos Chips, die mit Soitecs proprietärer Wafer-Technologie hergestellt wurden. Zu Soitecs Kunden zählen unter anderem große Chipproduzenten wie Samsung und GlobalFoundries.

Um Soitecs Position und die Bedeutung von SOI-Wafern in der Halbleiterindustrie zu verstehen, lohnt sich ein kleiner Exkurs in diese faszinierende Industrie.

Exkurs: Die Wertschöpfungskette der Halbleiterindustrie

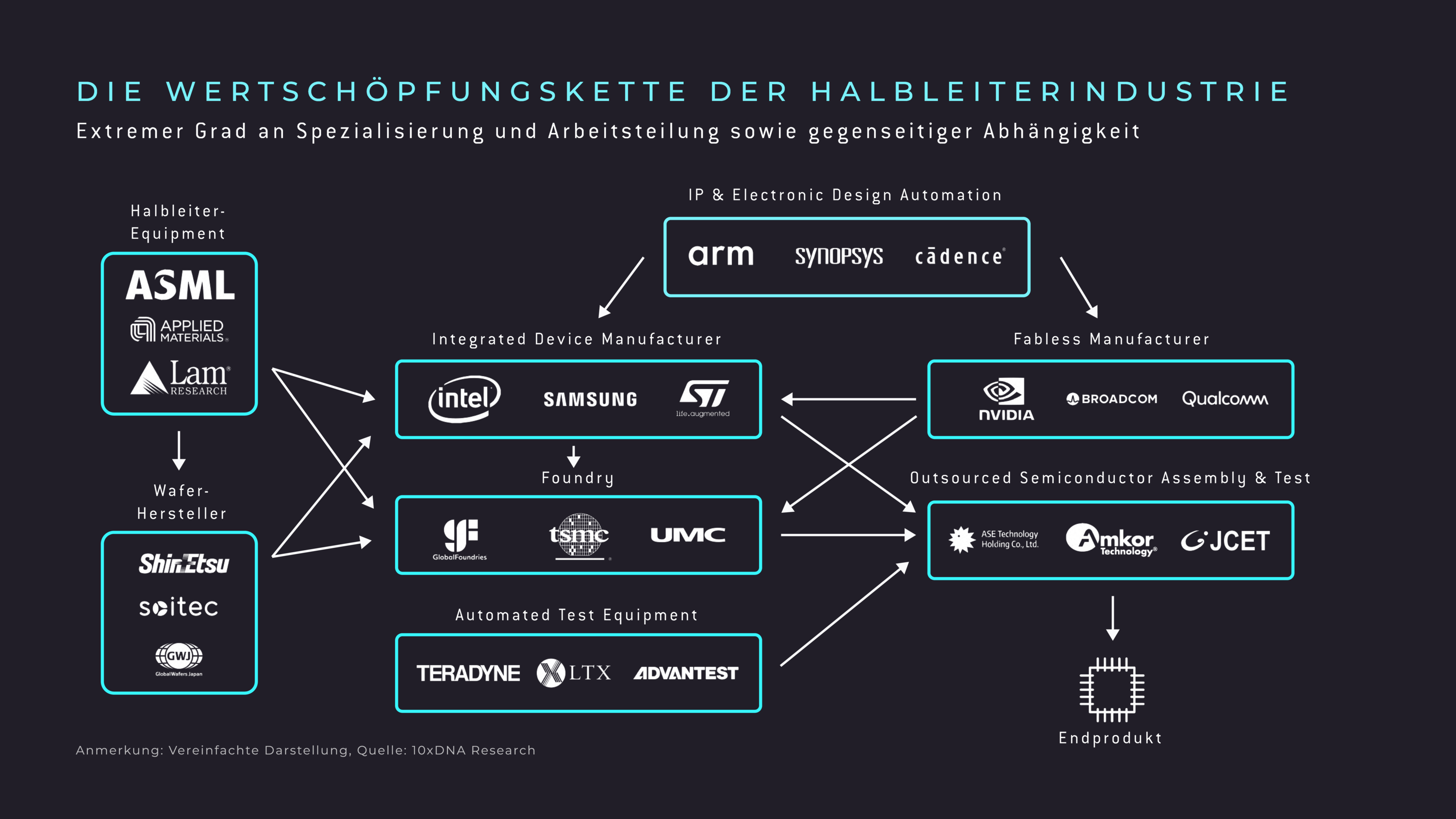

Die Halbleiterindustrie ist eine überaus komplexe Branche, die sich über die vergangenen Jahrzehnte immer weiter in Richtung extremer Spezialisierung der beteiligten Unternehmen auf bestimmte Bereiche der Wertschöpfungskette und damit einhergehend einer klar definierten Arbeitsteilung sowie starker gegenseitiger Abhängigkeit entwickelt hat. Soitec nimmt dabei als Wafer-Produzent eine Schlüsselposition ein. Die untere Grafik zeigt einen stark vereinfachten Überblick über die Wertschöpfungskette in der Halbleiterbranche bis zum fertigen Endprodukt, dem Computerchip, inklusive einiger relevanter Beispielunternehmen bei jeder Station.

Die gezeigten Stationen in der Wertschöpfungskette haben folgende Rollen:

-

Wafer-Hersteller

Wafer-Produzenten wie Soitec beliefern Integrated Device Manufacturers und Foundries mit den Substraten aus Halbleitermaterial (z.B. Silizium), auf denen die Chips gebaut werden. -

Halbleiter-Equipment

Zulieferer in diesem Bereich liefern Maschinen an Integrated Device Manufacturers, Foundries und Wafer-Hersteller, mit denen diese dann Halbleiter-Chips bzw. Wafer produzieren. Die Equipment-Zulieferer sind ihrerseits oft selbst sehr abhängig von spezialisierten Zulieferern für einzelne Komponenten. -

Integrated Device Manufacturer (IDMs)

IDMs designen ihre eigenen Chips und produzieren diese auch in eigenen Werken (sogenannte Fabs). Teilweise nutzen IDMs zusätzlich auch spezialisierte Foundries für die Produktion ihrer Chips und/oder betreiben ein eigenes Foundry-Geschäft. -

Foundry

Foundries spezialisieren sich auf die Produktion von Halbleiter-Chips, d.h. sie designen keine eigenen Chips, sondern werden von anderen Unternehmen mit der Produktion der Chips beauftragt. -

Fabless Manufacturer (FM)

FMs entwickeln und designen eigene Chips, stellen diese jedoch nicht selbst her, sondern lagern die Produktion an IDMs mit eigenem Foundry-Geschäft oder spezialisierte Foundries aus. -

Intellectual Property (IP) und Electronic Design Automation (EDA)

IP-Firmen lizenzieren ihr geistiges Eigentum (englisch: IP), beispielsweise zu Prozessor-Architekturen, an IDMs und Fabless-Firmen aus und diese nutzen die IP dann für ihre eigenen Chip-Designs. EDA-Firmen liefern Software, die zur Planung der komplexen mikroelektronischen Schaltpläne und für die Übertragung in ein physisches Design der Chips genutzt wird. -

Outsourced Semiconductor Assembly and Test (OSAT)

OSAT-Firmen montieren, verpacken und testen die von Foundries und IDMs produzierten Chips vor der Auslieferung an die Endkunden. -

Automated Test Equipment (ATE)

ATE-Hersteller produzieren Geräte und Anlagen, mit denen OSAT-Firmen Chips automatisiert auf Funktionsfähigkeit testen.

Für technisch Interessierte erläutern wir im folgenden Abschnitt die technischen Hintergründe von SOI-Wafern inklusive der Vor- und Nachteile, die sie für Computerchips mit sich bringen. Wer sich nur für unsere Investmenthypothesen interessiert und/oder Vorwissen zu SOI-Technologie hat, kann diesen Abschnitt überspringen.

Was hat es mit SOI-Wafern auf sich?

Um Soitecs SOI-Wafer zu verstehen, ist es zunächst wichtig, Wafer im Allgemeinen zu beleuchten.

Was sind Wafer?

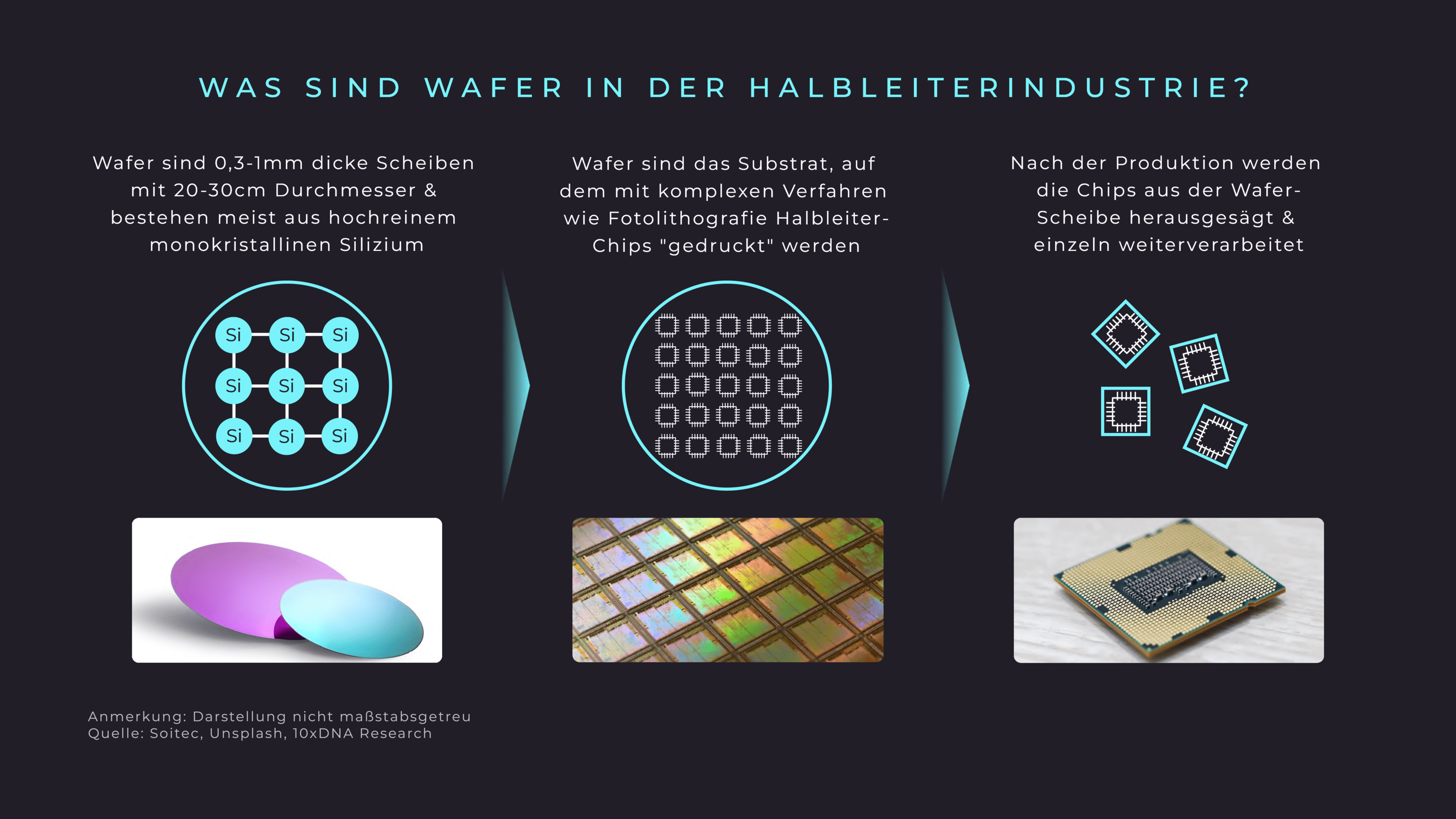

Wafer sind meistens kreisrunde ca. 0,3-1mm dicke Scheiben aus Silizium, seltener auch aus Galliumarsenid, Siliziumkarbid oder anderen Halbleitermaterialien. Wafer haben üblicherweise einen Durchmesser von 200-300mm und bilden das Substrat für die Produktion von Halbleiterchips jeglicher Art. Die integrierten Schaltkreise in Computerchips werden mithilfe von Beschichtungsverfahren und Fotolithografie auf die Oberfläche des Wafers “aufgedruckt”.

Wafer werden heute meist über das Czochralski-Verfahren hergestellt, bei dem zunächst ein großer Siliziumkristall, genannt Ingot, aus einer Schmelze gezüchtet wird, aus dem danach einzelne Wafer-Scheiben herausgeschnitten werden. Anschließend werden die Wafer weiterverarbeitet, die Oberflächen poliert und ggf. Dotierung erzeugt.

Der Prozess ist technisch komplex, weil die Halbleiterindustrie extrem hohe Anforderungen an die Qualität des Materials stellt. So darf der Anteil von Unreinheiten im Wafer nicht höher als 0,0000001% (ein Teil pro Milliarde) sein, die Oberfläche muss absolut glatt sein, die Dicke überall gleichförmig und der Wafer muss aus einem nahezu perfekten Monokristall ohne Defekte im Atomgitter bestehen. Unreinheiten, Abweichungen oder Defekte im Wafer können dazu führen, dass ein darauf produzierter Chip nicht wie geplant funktioniert, was für IDMs und Foundries inakzeptabel ist.

Aufgrund der technischen Komplexität, des hohen Kostendrucks und hoher Skaleneffekte ist die globale Waferindustrie inzwischen stark konsolidiert. Fünf große Spieler dominieren mit ca. 90% Marktanteil: Shin-Etsu, Sumco (beide aus Japan), GlobalWafers (Taiwan), Siltronic (Deutschland) und SK Siltron (Südkorea). Soitec ist eines der größten Unternehmen in den verbleibenden 10% des Marktes. Insgesamt wird der Umsatz des Wafer-Markts auf ca. 13 Milliarden USD jährlich geschätzt. Das Wachstum dürfte sich bis 2030 am Gesamthalbleitermarkt orientieren, was auf durchschnittlich 7% pro Jahr geschätzt wird, jedoch leicht stärker ausfallen.

Was sind SOI-Wafer?

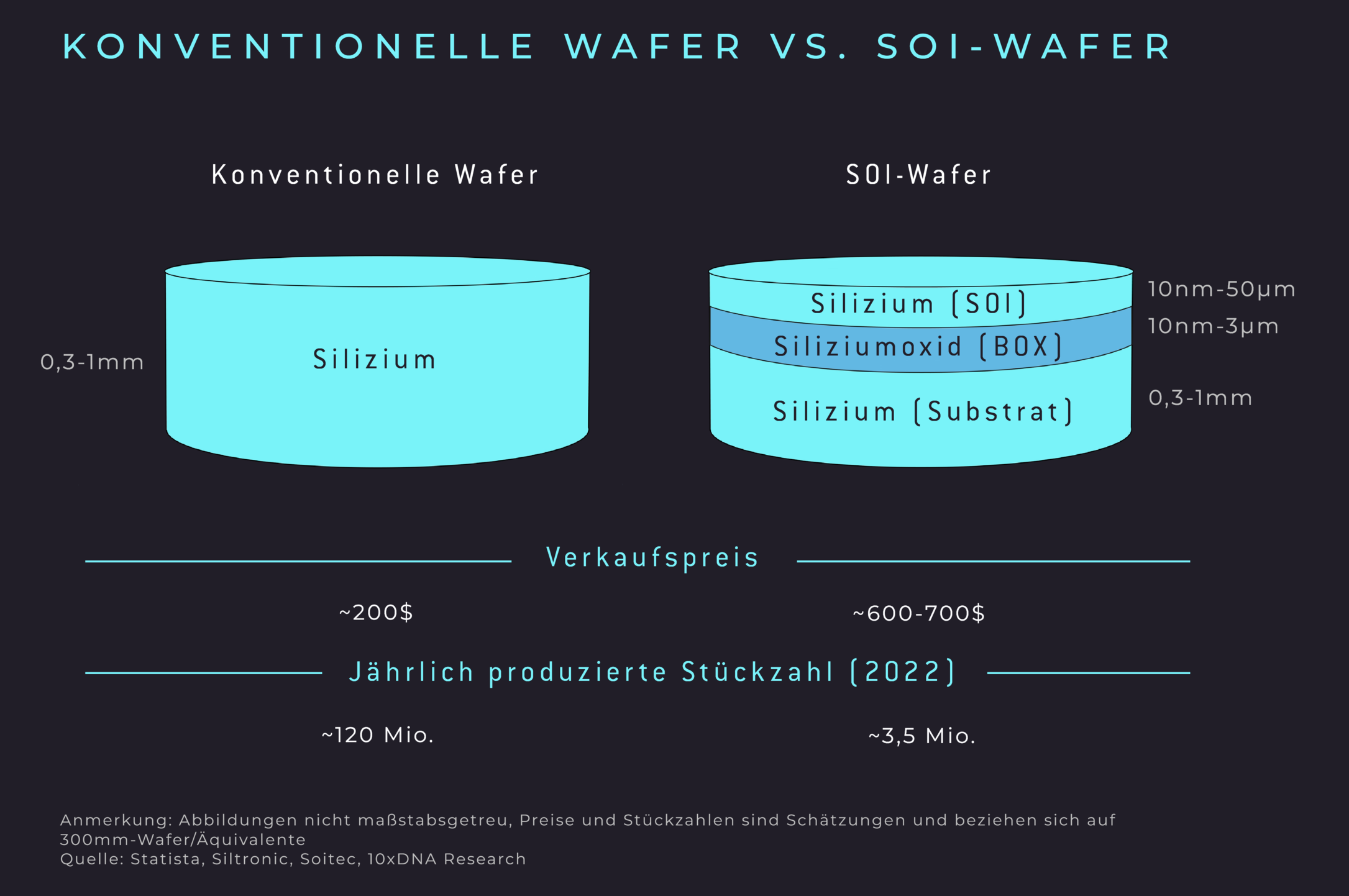

Silicon-On-Insulator-Wafer sind eine besondere Art von Silizium-Wafern. Der SOI-Wafer ist aus drei Ebenen aufgebaut: einer dünnen Siliziumschicht, die sogenannte SOI-Schicht, einer ebenfalls dünnen Siliziumoxid-Schicht und einer dicken Substratschicht aus Silizium (siehe Grafik). Die Siliziumoxid-Schicht wird auch als BOX-Schicht bezeichnet (BOX als Abkürzung für englisch “Buried Oxide”). Anders als Silizium, welches ein Halbleiter ist, ist Siliziumoxid elektrisch isolierend, d.h. es können in ihr keine Elektronen fließen. Somit trennt die BOX-Schicht die SOI-Schicht elektrisch vom Rest des Wafers, was der entscheidende Unterschied zu konventionellen Wafern ist.

SOI-Wafer sind deutlich komplexer in der Herstellung als konventionelle Wafer. Statt einer Schicht, wie bei konventionellen Wafern, müssen drei hochwertige, gleichmäßige Schichten produziert und nahezu defektfrei miteinander verbunden werden. Die Dicke der SOI- und BOX-Schichten ist abhängig von den technischen Anforderungen des Chips und liegen teils nur im Bereich von 10 Nanometern. Zum Vergleich: Ein menschliches Haar ist ungefähr 5.000 Mal dicker. Die Fehlertoleranz liegt teilweise bei nur 0,4nm und damit in der Größenordnung einzelner Atome, was die unglaublichen Anforderungen an die Präzision bei der Herstellung verdeutlicht.

Was sind Vor- und Nachteile von SOI-Wafern?

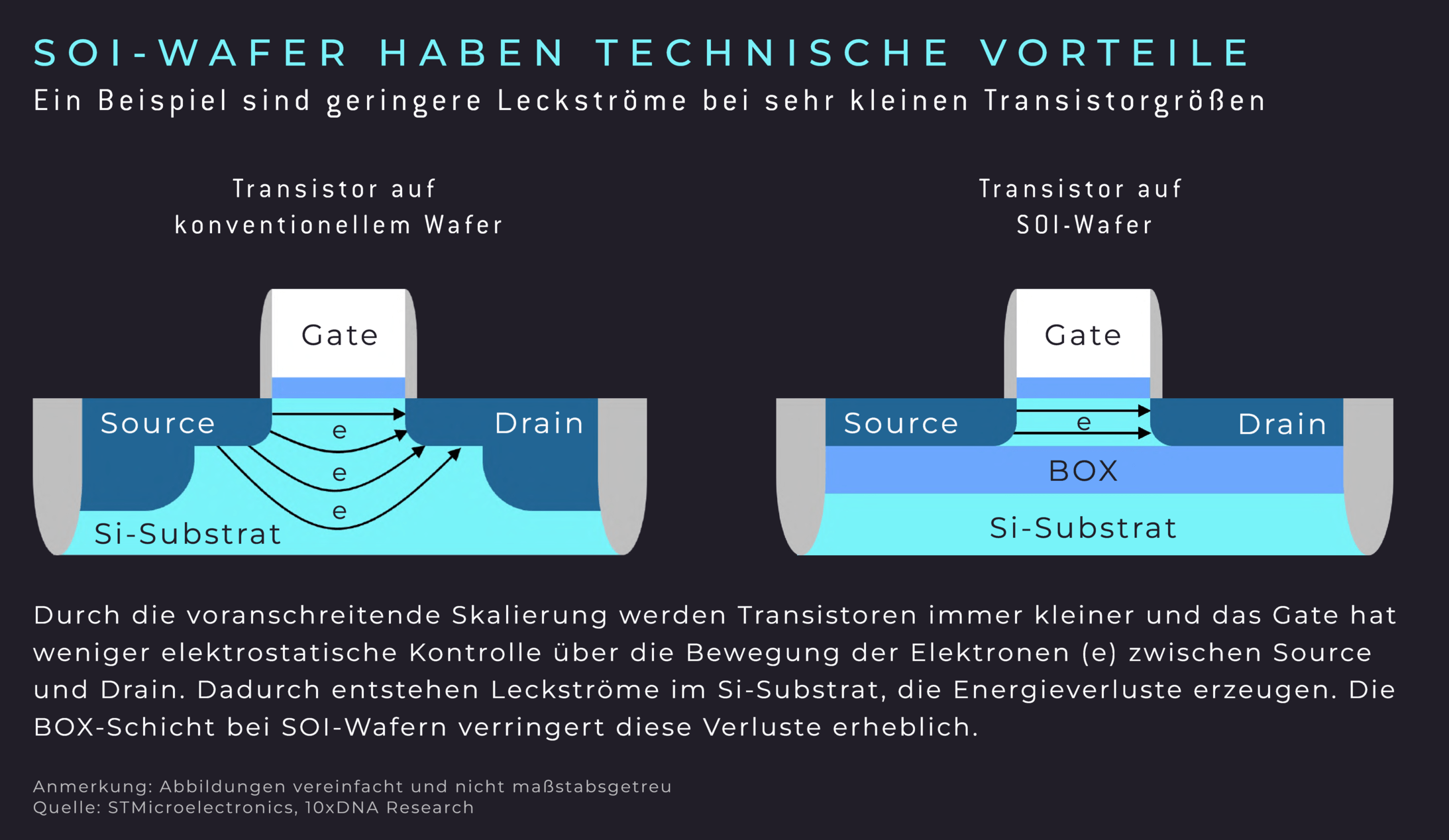

Transistoren bilden den fundamentalen Baustein nahezu aller Arten von Computerchips. Ihre physikalischen Eigenschaften und damit die Leistungsfähigkeit des gesamten Chips hängen zum einen von den Details der Transistorarchitektur ab. Zum anderen sind aber auch die Eigenschaften und der Aufbau des Wafers relevant, auf dem sie gebaut sind. Hierin unterscheiden sich konventionelle Wafer deutlich von SOI-Wafern. Letztere führen zu folgenden Hauptvor- und -nachteilen in SOI-basierten Chips:

Vorteile

-

Geringerer Energieverbrauch

Bei konventionellen Chips können Leckströme insbesondere bei sehr kleinen planaren Technologieknoten unter 28nm ein massives Problem sein. Die BOX-Schicht bei SOI-Chips verhindert diese Leckströme unter den Transistoren (siehe Grafik), was die Wärmeentwicklung und Energieverluste des Chips stark verringert. Hinzu kommt, dass der Stromkanal des Transistors, d.h. der stromführende Bereich zwischen Source und Drain, aufgrund der Eingrenzung durch die BOX-Schicht dünner ist. Dadurch kann der Transistor durch geringere Schwellenspannungen ein- und ausgeschaltet werden, was ebenfalls den Energieverbrauch senkt. -

Umschalten zwischen unterschiedlichen Betriebsmodi

SOI-Chips erlauben es besser als andere Chips “Body-Biasing” anzuwenden. Dies ermöglicht es, den Chip, je nach Bedarf, zwischen einem Hochleistungsmodus (hohe Leistung, hoher Energieverbrauch) und einem Energiesparmodus (niedrige Leistung, niedriger Energieverbrauch) umzuschalten. Dies ist beispielsweise bei IoT-Geräten von Vorteil, die oft nur kurzzeitig hohe Leistung liefern müssen und ansonsten vor allem einen niedrigen Energieverbrauch und damit eine lange Batterielebensdauer haben sollen. -

Bessere Analog-Eigenschaften

SOI-basierte Chips haben in aller Regel bessere Eigenschaften bei der Verarbeitung von analogen (d.h. nicht digitalen) Signalen, z.B. Radiofrequenzwellen bei 5G. Ein Grund dafür ist die geringere Variabilität bei der Produktion der SOI-Chips. Bei Chips auf konventionellen Wafern muss der Kanal mit Fremdatomen dotiert werden, was unweigerlich zu Fluktuationen führt. Bei SOI-Chips hingegen bleibt der Kanal undotiert, was die für Analogsignale entscheidenden gleichbleibenden Eigenschaften zwischen den Transistoren sicherstellt. -

Höhere Leistungsfähigkeit

Da die BOX-Schicht den Transistor elektrisch vom Rest des Wafers trennt, haben SOI-Chips eine deutlich niedrigere parasitäre Kapazität. Dies erlaubt es, die Transistoren schneller umzuschalten und erhöht so die Leistungsfähigkeit ceteris paribus. Auch die bereits erwähnte geringere Wärmeentwicklung erhöht die Leistungsfähigkeit, da sie den Kühlbedarf des Chips verringert.

Nachteile

-

Höhere Wafer-Kosten

SOI-Wafer sind aufgrund des aufwendigen Herstellungsprozesses deutlich teurer als konventionelle Wafer. Zwar werden die genauen Verkaufspreise in der Industrie nicht offen kommuniziert, sie dürften für SOI-Wafer jedoch im Bereich von 600-700$ und für konventionelle Silizium-Wafer bei ca. 200$ liegen (jeweils für 300mm-Wafer). In der preissensiblen Halbleiterindustrie ist das ein erheblicher Unterschied. Der Anteil der Waferkosten an den Gesamtkosten eines Chips ist jedoch oft relativ gering (5-10%) und aufgrund der zuvor genannten Vorteile und dem höheren Wert der SOI-basierten Chips kann der höhere Preis in vielen Anwendungen gerechtfertigt sein. -

Eigenes Ökosystem und unklare technologische Roadmap

Die Herstellung von SOI-Chips ist im Prinzip kompatibel mit den konventionellen planaren Herstellungsprozessen für CMOS-Chips, jedoch gibt es in der Praxis Unterschiede, die ein eigenes Ökosystem für EDA-Software, Schaltkreis-IP, Prozess-Knowhow etc. nötig machen. Ein solches Ökosystem wurde zwar über die letzten Jahre von den im SOI-Bereich aktiven Firmen (z.B. STMicroelectronics, Samsung, GlobalFoundries) und Forschungsinstituten aufgebaut, es ist jedoch noch nicht so ausgereift und weit verbreitet wie das Ökosystem konventioneller Chips, was eine klare Umstiegshürde für Unternehmen darstellt. Auch die technologische Roadmap zur weiteren Skalierung ist weniger klar definiert als in anderen Bereichen der Halbleiterindustrie.

Wichtig: Die genannten Vor- und Nachteile gelten nur für den Vergleich von SOI-Chips mit anderen mit planaren Verfahren hergestellten Chips mit ähnlichen Dimensionen auf konventionellen Wafern. Der Vergleich mit 3D-Designs mit FinFETs oder GAAFETs auf konventionellen Wafern ist komplexer und muss gesondert betrachtet werden.

Investmenthypothesen

Unsere Entscheidung Soitec ins 10xDNA-Portfolio aufzunehmen basiert maßgeblich auf den folgenden drei Investmenthypothesen:

SOI-Technologie wird in der Halbleiterindustrie stark an Bedeutung gewinnen

Soitec ist der führende Anbieter von SOI-Wafern und wird dies auch langfristig bleiben

Der Markt für SOI-Wafer wird auf absehbare Zeit angebotslimitiert bleiben und Soitec hohe Margen ermöglichen

1. SOI-Technologie wird in der Halbleiterindustrie stark an Bedeutung gewinnen

In der Halbleiterindustrie gibt es einen konstanten Druck, alle Arten von Chips kontinuierlich zu verbessern, d.h. die Kosten zu senken und die Leistungsfähigkeit über die Transistordichte zu erhöhen. In der Vergangenheit geschah dies vorwiegend durch die kontinuierliche Verkleinerung der physischen Strukturen von planaren Transistoren gemäß “Moore’s Law”. Demnach verdoppelt sich die Transistordichte auf Computerchips alle 24 Monate und die Kosten pro Transistor (bzw. pro Rechenleistung) sinken kontinuierlich. Durch diese Entwicklung ist heute jedes Smartphone um ein Vielfaches leistungsstärker als der stärkste Supercomputer von vor ein paar Jahrzehnten.

Bis zum 28nm-Technologieknoten, der seit 2013 genutzt wird, galt Moore’s Law für so gut wie alle Arten von Chips uneingeschränkt. Unterhalb von 28nm steigt die Transistordichte zwar weiter, jedoch sinken die Kosten pro Transistor nicht mehr, sondern steigen wieder an, weil die Produktionsprozesse deutlich komplizierter werden. Hinzu kommen spätestens ab 14nm unüberwindbare physikalische Grenzen bei planaren Transistoren auf konventionellen Wafern, weil das Gate des Transistors wie in obiger Grafik gezeigt bei solch extrem kleinen Dimensionen nicht mehr ausreichend elektrostatische Kontrolle über den Kanal ausüben kann. Dadurch werden u.a. Leckströme unkontrollierbar und der Transistor kann nicht mehr wie vorgesehen ein- und ausgeschaltet werden. Dies macht bei noch kleineren Technologieknoten aufwändige 3D-Designs mit FinFETs oder GAAFETs nötig, was zwar bei vielen Chips weitere Skalierung ermöglicht, den Aufwand und die Kosten aber immer weiter erhöht. Zusammengefasst kann die Weiterentwicklung der Chiptechnologie bei sehr kleinen Technologieknoten heute nicht mehr auf konventionellen Wafern weitergetrieben werden, ohne die Kosten pro Transistor zu erhöhen. Chiphersteller haben zwei Optionen, um ihre Produkte dennoch unterhalb von 28nm weiter zu verbessern:

- Weitere Skalierung auf konventionellen Wafern durch 3D-Designs mit FinFETs/GAAFETs

- Umstieg auf SOI-Technologie und Skalierung mit planaren Transistoren auf SOI-Wafern

Die Entscheidung für eine der beiden Optionen ist komplex und muss für jede Anwendung einzeln getroffen werden, weil sie unter anderem von folgenden (teils untereinander abhängigen) Faktoren abhängt:

-

Technische Aspekte und Anforderungsprofil des Chips

Chips haben unterschiedliche Anforderungsprofile und beide Optionen haben technische Vor- und Nachteile, z.B. beim Energieverbrauch, der erzielbaren Transistordichte oder der Sensibilität gegenüber Temperaturschwankungen während des Betriebs. All diese Faktoren müssen gegeneinander abgewogen werden. So kann es sein, dass beispielsweise für einen 5G-Chip in Smartphones der Weg mit SOI-Technologie sinnvoller ist, wohingegen für einen GPU-Chip für PCs ein 3D-Design auf konventionellen Wafern die beste Wahl ist. -

Kosten

Hier sind zum einen die Entwicklungskosten relevant, die sich zwischen den beiden Optionen unterscheiden können und insbesondere beim Umstieg von einer Technologie auf die andere kurzfristig ein großer Faktor sein können. Zum anderen variieren die eigentlichen Produktionskosten der Chips in Abhängigkeit von der technischen Details. Grund dafür sind beispielsweise die höheren Waferkosten bei SOI-Chips, demgegenüber die größere Anzahl an nötigen Herstellungsschritten und die Komplexität bei 3D-Designs steht. Auch die geplante Stückzahl der Chips hat einen Einfluss, da sich manche Mehrkosten durch große Skaleneffekte rechtfertigen lassen, wenn dadurch technische Vorteile erzielt werden. -

Verfügbare Foundry-Partner und Zulieferer

Je nachdem, für welche Option sich ein Chiphersteller entscheidet, begibt er sich in unterschiedliche Abhängigkeiten zu Foundries und/oder Zulieferern. Fällt die Wahl auf 3D-Designs auf dem neusten 5nm-Technologieknoten, so stehen aktuell nur noch TSMC und Samsung als Foundry-Partner zur Verfügung. Diese fokussieren sich vor allem auf große Chiphersteller, was für kleinere Chiphersteller problematisch sein kann. Fällt die Wahl auf SOI bei etwas größeren Technologieknoten, so beginnt eine Abhängigkeit von Soitec als SOI-Waferzulieferer mit knapp 80% Marktanteil. Beides muss strategisch abgewogen werden, da diese Abhängigkeit in Zukunft gar nicht oder nur mit hohem Aufwand wieder aufgelöst werden kann.

Anwendungsfelder

Angesichts dieser Faktoren sind generelle Aussagen darüber, für welche Arten von Chips sich SOI-Technologie etablieren wird, schwierig. Aus unserer Sicht wird SOI-Technologie ein Werkzeug von mehreren sein, um den technologischen Fortschritt bei Computerchips weiter voranzutreiben. Es gibt jedoch vor allem drei Bereiche, für die sich SOI-Technologie besonders gut eignet:

-

Mobile Kommunikation

Hier ist vor allem der Smartphone-Markt zu nennen, wo die SOI-Vorteile bei analogen RF-Chips und dem Energieverbrauch sehr relevant sind. In Bezug auf die Anzahl der jährlich verkauften Geräte stagniert der Smartphone-Markt zwar, der Anteil von 5G-Geräten nimmt aber massiv zu. Bereits heute stecken in nahezu allen 4G-Smartphones RF-Chips auf SOI-Wafern. Neue 5G-Smartphones benötigen ungefähr die doppelte Menge an SOI-Waferfläche. Ähnliches gilt für 5G-Funkmasten. Ein prominentes Beispiel für die Anwendung von SOI-Technologie ist Googles Pixel 6 Smartphone, das SOI-basierte 5G-Chips verwendet. -

Automobile Anwendungen

Das Auto der Zukunft wird elektrisch, autonom und vernetzt sein. All diese Eigenschaften verlangen neuartige Chips, die insbesondere in Sachen Energieeffizienz und der Kombination von digitalen und analogen Signalen, sogenannte Mixed Signals, hohe Anforderungen stellen. Diese Eigenschaften bedient SOI optimal und gleichzeitig ist der Markt für automobile Chips einer der am stärksten wachsenden Sektoren der Halbleiterindustrie. -

Smart Devices und Internet-of-Things (IoT)

Bei vielen Smart Devices und Geräten im IoT kommt es oft weniger auf die reine Rechenleistung der Chips an, sondern vor allem auf einen niedrigen Energieverbrauch, die Verarbeitung von Mixed Signals und die Möglichkeit des Umschaltens zwischen Betriebsmodi. In diesen drei Bereichen hat SOI seine Stärken gegenüber konventionellen Chips, weshalb die Technologie große Verbreitung in diesen Wachstumsmärkten findet.

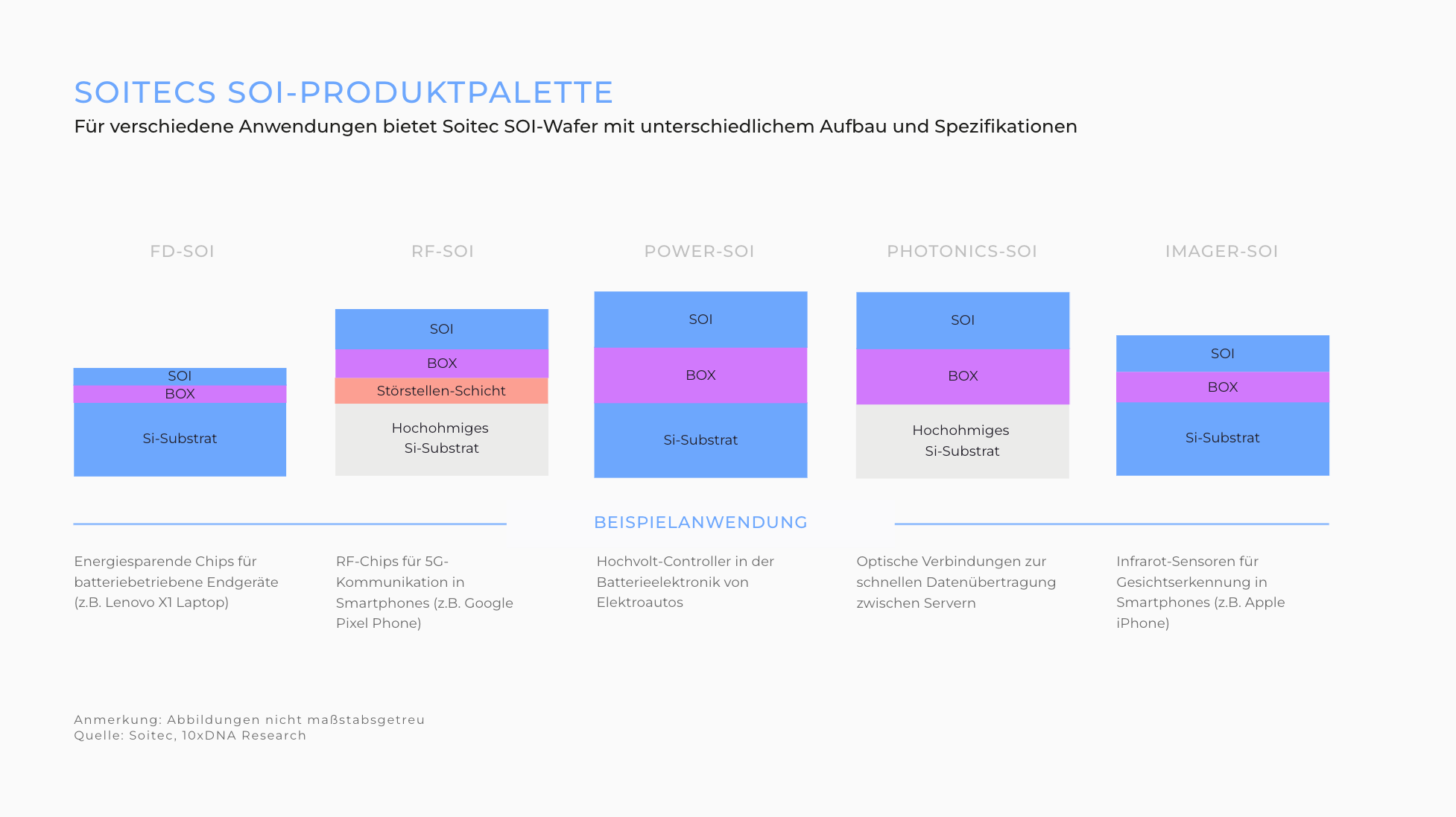

Soitecs Produktpalette ist auf die drei genannten Bereiche sowie weitere SOI-freundliche Anwendungen zugeschnitten.

Soitec erwartet, dass seine Zielmärkte bis 2030 insgesamt mit ca. 20% jährlichen Wachstum deutlich stärker als der Gesamthalbleitermarkt mit ca. 7% p.a. wachsen werden. Entsprechend wird auch die SOI-Technologie stark an Bedeutung gewinnen. Nach unseren eigenen Analysen und Gesprächen mit Industrieexperten gehen wir davon aus, dass bis zu 50 Prozentdes gesamten Halbleitermarktes theoretisch für SOI-Technologie in Frage kommt, was großes langfristiges Wachstumspotenzial eröffnet und entsprechend positive Aussichten für Soitec als dominierenden SOI-Waferzulieferer bedeutet. Auch im kürzlich veröffentlichten “Chips Act” der Europäischen Union wird SOI explizit als Schlüsseltechnologie für die energieeffizienten Chips der Zukunft genannt, was weitere Unterstützung von politischer Seite wahrscheinlich macht.

Bereits heute investiert Soitec in die nächsten Generationen von Technologien, z.B. SmartSiC™ zur Herstellung von Siliziumkarbid-Wafern, die weiteres Wachstum in der ferneren Zukunft versprechen. Hier ist jedoch die weitere technologische Entwicklung und die Verbreitung beispielsweise in Elektroautos noch deutlich weniger absehbar als bei SOI.

Risiken

Neue Innovationen in der Halbleiterproduktion (z.B. 3D-Chipdesigns mit GAAFETs) könnten sich als vorteilhaft in Bereichen herausstellen, in denen aktuell noch SOI die erste Wahl ist, und damit die Verbreitung von SOI-Technologie bremsen oder reduzieren. Wir sehen SOI und 3D-Verfahren technologisch gesehen jedoch als komplementär an und halten dieses Risiko daher für gering. Entscheidend wird sein, dass sich durch R&D-Arbeit im Bereich SOI genau wie in anderen Bereichen eine klare Skalierungs-Roadmap herauskristallisiert, die Chipherstellern die Sicherheit gibt, dass sich ein Umstieg auf SOI langfristig lohnen wird.

Ein weiteres Risiko ist der langsame Ausbau des SOI-Ökosystems und die aktuell noch limitierte Anzahl an Foundries mit SOI-Angeboten, was zumindest auf absehbare Zeit manche Chiphersteller noch davon abhalten könnte, SOI-Technologie zu nutzen.

2. Soitec ist der führende Anbieter von SOI-Wafern und wird dies auch langfristig bleiben

Ähnlich wie das niederländische ASML im Bereich EUV-Lithografie, hat Soitec im Markt für SOI-Wafer eine extrem dominante Stellung inne. Laut eigenen Angaben hatte das Unternehmen über die letzten Jahre einen Marktanteil von 77%. Den Großteil des verbleibenden SOI-Marktes teilen die Wafer-Hersteller Shin-Etsu und GlobalWafers unter sich auf, welche beide jedoch Soitecs Technologie auslizensieren und dafür Lizenzgebühren zahlen. Im Fiskaljahr 2022 betrugen die Lizenzgebühren 30 Millionen Euro und machten damit ca. 3,5% von Soitecs Umsatz aus.

Der Grund für Soitecs dominante Stellung liegt in der proprietären SmartCut-Technologie, die heute die Standardmethode zur Herstellung von SOI-Wafern ist. Diese wurde 1991 von Michael Bruel am CEA-Leti erfunden, nach Gründung Soitecs in 1992 das erste Mal industrialisiert und seither über mehr als 30 Jahre weiterentwickelt und verfeinert. Heute liefert diese Technologie, die im Grunde ein atomares Skalpell darstellt, die SOI-Wafer mit der höchsten Qualität weltweit.

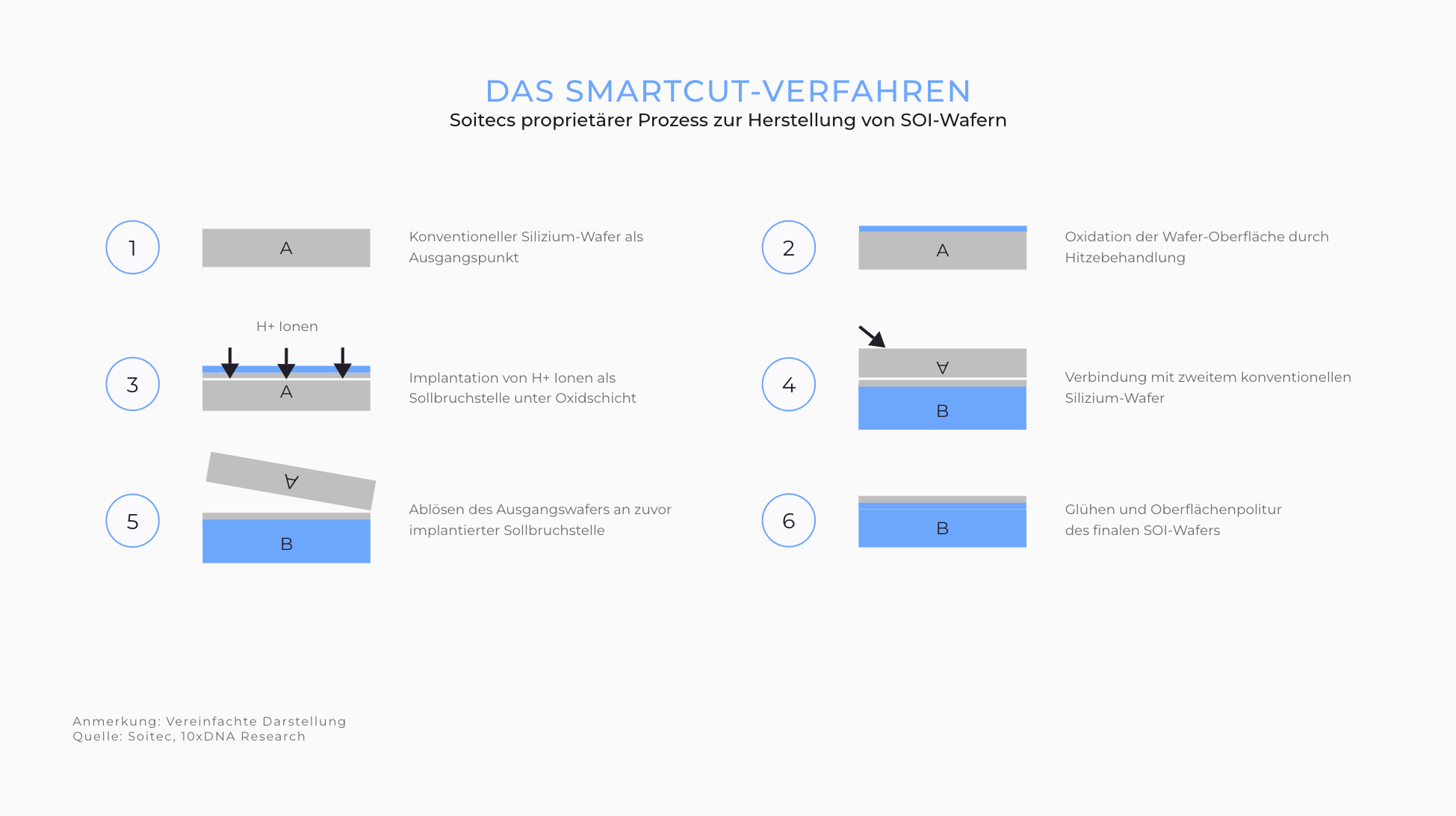

Wie in der untenstehenden Grafik gezeigt, besteht der SmartCut™-Prozess im Wesentlichen aus sechs Schritten:

- Der Prozess startet mit einem konventionellen Wafer aus monokristallinem Silizium als Ausgangspunkt.

- Die Oberfläche des Wafers wird mittels eines thermischen Verfahrens oxidiert. Die entstehenden Oxidschicht aus SiO2 ist ca. 10nm-3µm dick, was der gewünschten Dicke der BOX-Schicht entspricht.

- Der Wafer wird mit H+ Ionen beschossen, die eine genau festgelegte Energie (d.h. Geschwindigkeit) haben. Die H+ Ionen dringen bis in eine gewünschte Tiefe unter die Oxidschicht in den Wafer ein und erzeugen Defekte im Kristallgitter des Wafers. Die Eindringtiefe, üblicherweise 10nm-50µm, entspricht der späteren Dicke der SOI-Schicht. Auf diese Art wird eine Sollbruchstelle erzeugt, die in den nächsten Schritten benötigt wird.

- Der Ausgangswafer mit der Oxidschicht wird nun umgedreht und mit einem zweiten konventionellen Wafer über Van-der-Waals-Kräfte bei Raumtemperatur verbunden. Durch Wärmebehandlung werden anschließend kovalente Bindungen erzeugt und so die Verbindung weiter verstärkt.

- Nach einer weiteren Erhitzung auf mehrere hundert Grad wird der Ausgangswafer nun an der zuvor implantierten Sollbruchstelle abgelöst, sodass nur noch die ca. 10nm-50µm dicke Siliziumschicht und die BOX-Schicht zurückbleibt. Die SOI-Struktur liegt nun vor und der Wafer ist bereit für die finalen Bearbeitungsschritte.

- Abschließend wird der erzeugte SOI-Wafer noch geglüht und poliert, um die finalen Eigenschaften für den Verkauf an Kunden zu erzeugen.

Diesen Prozess, der in Reinräumen der höchsten Kategorie abläuft, mit all seinen unzähligen technischen Herausforderungen in den Griff zu bekommen, ist extrem komplex. Wie bei konventionellen Wafern kann jeder ungewollte Defekt, jede Unreinheit und jede Abweichung von den Spezifikationen den Wafer für die Foundries und IDMs unbrauchbar machen.

Soitec hat inzwischen über 3.700 aktive Patente, die Aspekte des SmartCut-Prozesses selbst sowie andere Entwicklungen weitreichend schützen. Der Patentschutz, den das Unternehmen allein im vergangenen Jahr mit über 280 Anmeldungen weiter ausgebaut hat, und die jahrzehntelange Erfahrung mit der Komplexität des Verfahrens stellen aus unserer Sicht einen klaren Wettbewerbsvorteil für Soitec und eine erhebliche Eintrittsbarriere für andere Unternehmen dar. Zusammen mit den konstant hohen Ausgaben für Forschung und Entwicklung (11% des Umsatzes im Fiskaljahr 2022) wird dies Soitecs starke Position im Markt langfristig garantieren. Dass selbst deutlich größere Wafer-Hersteller wie Shin-Etsu und GlobalWafers Soitecs Technologie auslizenzieren statt sie selbst zu entwickeln, ist aus unserer Sicht ein weiteres Zeichen für Soitecs Technologieführerschaft.

Risiken

Wie immer ist es möglich, dass neue Technologien entwickelt werden und Innovationen auf den Markt kommen, die Soitecs SmartCut-Prozess Konkurrenz machen können. Da aktuell eine solche fundamentale Veränderung jedoch nicht absehbar ist und die Halbleiterindustrie solche Innovationen erfahrungsgemäß auch nur nach vielen Jahren Vorlauf adaptiert, sehen wir dieses Risiko mittelfristig als gering an.

Weitere Risiken, die in der Halbleiterindustrie immer auftreten können und Soitecs Erfolg behindern können, sind gestörte Lieferketten und unerwartete Verzögerungen bei der Skalierung von Anlagen und Prozessen. Aktuell sehen wir bei Soitec keine Hinweise darauf, aber werden dies weiter konstant beobachten.

3. Der Markt für SOI-Wafer wird auf absehbare Zeit angebotslimitiert bleiben und Soitec hohe Margen ermöglichen

Seit Beginn der Corona-Pandemie herrscht in der Halbleiterindustrie eine angespannte Lage in den Lieferketten und viele Industriebetriebe wie z.B. VW mussten ihre Produktion aufgrund akuten Chipmangels vorübergehend pausieren. Ein Grund dafür war und ist das limitierte Angebot an konventionellen Wafern, das laut Herstellern wie Sumco noch Jahre anhalten wird.

Unsere Analysen und Expertengespräche haben ergeben, dass auch der Markt für SOI-Wafer auf absehbare Zeit weiterhin angebotslimitiert bleiben dürfte, d.h. die Nachfrage nach SOI-Wafern wird stärker steigen als die zur Verfügung stehende Produktionskapazität. Der Grund dafür ist zum einen, dass es, wie erwähnt, neben Soitec überhaupt nur wenige weitere Unternehmen gibt, die SOI-Wafer produzieren können. Zum anderen ist der Zubau von Kapazität aufgrund der technischen Komplexität langwierig und kapitalintensiv. Soitec plant seine Produktionskapazität bis 2026 gegenüber 2021 fast zu verdoppeln und hat für einen Großteil der neuen Kapazität bereits Abnahmeverträge mit Kunden geschlossen. CEO Paul Boudre bestätigte im April 2022 zudem in der Telefonkonferenz zu den Q4-Quartalsergebnissen, dass Soitec jeden zusätzlich produzierten Wafer auch verkaufen könnte, was ebenfalls das limitierte Angebot unterstreicht. Alles in allem erwarten wir aktuell nicht, dass sich an dieser Situation bis 2026 etwas grundlegend ändern wird.

Die Angebotsknappheit führt dazu, dass Soitec eine exzellente Verhandlungsposition bei neuen Abnahmeverträgen hat und hohe Verkaufspreise pro Wafer durchsetzen kann. Entsprechend konnte die EBITDA-Marge in den vergangenen Jahren immer weiter auf zuletzt über 35% gesteigert werden und erst kürzlich wurde auch die langfristige EBITDA-Margenausblick um 5 Prozentpunkte auf 40% nach oben korrigiert, was wir für realistisch halten. Damit ist Soitec heute bereits ähnlich profitabel wie ASML (ebenfalls 35% EBITDA-Marge in 2021) und wird die Profitabilität in Zukunft voraussichtlich weiter steigern können.

Risiken

Die erwartete Angebotsknappheit basiert auf der Annahme, dass die Nachfrage nach SOI-Wafern wie erläutert weiter steigen wird. Eine globale Rezession jedoch könnte den Halbleitermarkt ans Ganzes und damit auch die Nachfrage nach SOI-Wafern stark einbrechen lassen, was natürlich entsprechende Risiken für Soitec birgt.

Auf der anderen Seite, sollte die Angebotsknappheit bei SOI-Wafern zu stark werden, könnte dies ebenfalls manche Unternehmen davon abhalten, auf SOI-Technologie umzusteigen. Verständlicherweise versuchen Unternehmen, sich nicht zu sehr von kaum zu ersetzenden Zulieferern mit starker Preissetzungsmacht wie Soitec abhängig zu machen.

ESG

Wie bei all unseren Investments fließt auch Soitecs ESG-Bilanz in unsere Investmententscheidung mit ein. Soitec hat im Juni 2022 eine “BB”-Bewertung von MSCI, was einer Position im unteren Mittelfeld der Halbleiterindustrie entspricht. Wir sehen das Unternehmen positiver, erkennen jedoch weiteren Handlungsbedarf in der Zukunft.

Environment

In dieser Kategorie wird Soitec von MSCI als unterdurchschnittlich in der Halbleiterindustrie gesehen. Ein Hauptgrund dafür ist der relativ hohe Wasserverbrauch der aufwändigen SOI-Waferproduktion. Zwar hat Soitec bereits heute Initiativen eingeführt, die den Wasserverbrauch pro hergestellten Wafer seit 2015 um 40% und allein im letzten Jahr um 12,5% gesenkt haben. Wir sehen dies jedoch als einen Kernpunkt, der in Zukunft weiter verbessert werden muss.

Insgesamt sehen wir Soitec dennoch als umwelttechnisch nachhaltiges Investment. Zum einen können SOI-Wafer wie oben erläutert den Energieverbrauch von Computerchips signifikant senken und damit zur Energieeffizienz unserer Gesellschaft beitragen. Zum anderen hat sich Soitec ambitionierte eigene Emissionsziele gesetzt, um die Erderwärmung auf unter 1,5°C zu begrenzen, und wurde dafür von der SBTI-Initiative zertifiziert.

MSCIs deutlich negativere Sicht, lässt sich folgendermaßen erklären: MSCI wendet einen sogenannte “Best in Class” Ansatz an, bei dem immer Unternehmen aus derselben Industrie miteinander verglichen und dann relative Bewertungen vergeben werden. Dies ist unserer Ansicht nach in diesem Fall fragwürdig, weil MSCI in Soitecs Vergleichsgruppe auch Fabless Manufacturer wie NVidia und Broadcom führt, die keine eigene Produktion besitzen und daher offensichtlich geringeren Wasser- und Energiebedarf haben. Der Vergleich innerhalb der Halbleiterbranche ist daher im Bereich Umwelt nur bedingt aussagekräftig.

Social und Governance

In den Kategorien Social und Governance wird Soitec von MSCI als leicht über dem Durchschnitt der Halbleiterindustrie bewertet.

Im Bereich Governance liegt das Unternehmen nur leicht über dem Schnitt, Abzüge gibt hier beispielsweise aufgrund einer Geldstrafe gegen einen früheren Soitec-CFO, der das Unternehmen bereits 2019 verlassen hat und weil Soitec einen Teil seiner Produktion in Regionen der Welt hat, die tendenziell hohe Korruptionsraten haben. Als deutlich relevanter sehen wir die Kontroverse rund um den angekündigten CEO-Wechsel von Paul Boudre auf Pierre Barnabe Anfang 2022. Da sich die Situation danach im Soitec-Vorstand jedoch wieder beruhigt hat und einige der Missverständnisse aufgeklärt wurden, sehen wir dies aktuell nicht mehr als großes Problem an. Auch gibt es aktuell keine konkreten Hinweise auf weiteres Fehlverhalten des Managements und das Board ist aus unserer Sicht mit genügend unabhängigen Mitgliedern besetzt.

Im Bereich Social liegt klar über dem Industrieschnitt, was sich mit unserer Einschätzung deckt. Als positive Beispiele für Soitecs Einsatz für soziale Aspekte sind beispielsweise Initiativen im Bereich Chancengleichheit und Inklusion zu nennen.

Zusammengefasst sehen wir Soitec als ein Unternehmen mit guter, aber nicht überragender Bilanz in Sachen Nachhaltigkeit. Wir werden dies wie immer weiter beobachten und uns, wenn möglich, auf Generalversammlungen über unsere Stimmrechte für weitere Anstrengungen zur Verbesserung der ESG-Bilanz, insbesondere im Bereich Umwelt einsetzen.

Bewertung

Nach der Analyse der Technologie haben wir zukünftige Werttreiber für den Soitec-Aktienkurs identifiziert. Wesentliche Treiber ergeben sich hier aus der Quasi-Monopolstellung des Unternehmens in einem Zukunftsfeld der Halbleitertechnologie, der Preissetzungsmacht durch ein limitiertes Angebot im Markt und attraktive langanhaltende Trends wie die Verbreitung von 5G und die Nachfrage nach energieeffizienten Chips, die Wachstum treiben werden. Diese Faktoren sowie die beschriebenen Risiken haben wir in einer Discounted Cashflow Bewertung des Unternehmens reflektiert und kommen zu dem Ergebnis, dass die Soitec-Aktie aktuell ein attraktives Risiko-Rendite-Verhältnis aufweist.

Fazit

Soitec ist der führende Hersteller von SOI-Wafern mit einzigartigem technischen Knowhow, das seinen Kunden massive Fortschritte bei der weiteren Verbesserung von Computerchips und deren Anwendung in verschiedensten Zukunftsfeldern ermöglicht. Die identifizierten Werttreiber haben wir in einer Unternehmensbewertung reflektiert und halten die Soitec-Aktie aktuell für signifikant unterbewertet. Aus diesem Grund ist das Unternehmen Teil der 10xDNA-Fonds.

Wie seht ihr Soitec und die SOI-Technologie? Teilt ihr unsere Meinung oder seht ihr das Unternehmen und den Markt anders? Wir freuen uns über jede Art von Feedback! Schreibt uns über einen unserer Social-Media-Kanäle oder über info@10xdna.com.